我院熊晓明教授团队联合中国科学院半导体研究所张钊研究员团队在集成电路权威期刊《IEEE Transactions on Circuits and Systems--II: Express Briefs》,发表题为《A 6-64-Gb/s 0.41-pJ/bit Reference-Less PAM4 CDR Using a Frequency-Detection-Gain-Enhanced PFD Achieving 19.8-Gb/s/μs Acquisition Speed》的研究论文。

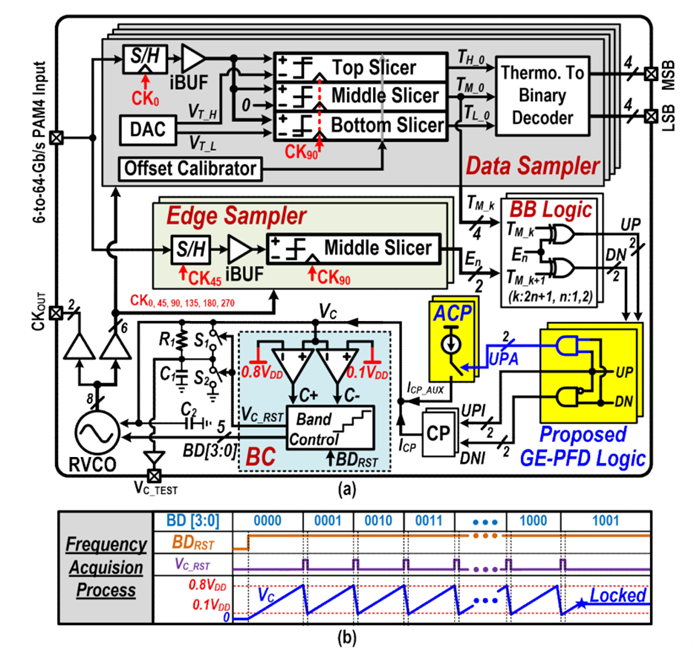

随着高性能计算、人工智能等新兴技术的快速发展,高速数据传输需求持续激增,四电平脉冲幅度调制信号因能在相同带宽下实现双倍数据速率,已成为高速串行链路的核心技术方向。而时钟数据恢复电路(Clock and Data Recovery,简称CDR)作为高速通信系统的核心模块,其性能直接决定数据传输的可靠性与能耗。传统CDR要么依赖参考时钟增加成本,要么存在频率捕获慢、功耗高、稳定性差等问题,难以适配汽车以太网、PCIe Gen6 等多场景的宽速率需求。针对上述挑战,团队提出了一种基于频率检测增益增强型相位频率检测器(命名为GE-PFD)的无参考PAM4 CDR 架构。该设计创新性地在经典Alexander bang-bang相位检测器基础上,仅增加两个逻辑门,配合辅助电荷泵,既省去了额外的频率检测器和时钟相位,又实现了捕获速度与环路稳定性的协同优化,能够快速完成频率捕获与相位锁定,大幅提升了频率检测增益。

流片后实测结果显示,该CDR芯片采用40-nm CMOS工艺实现,核心面积仅0.063 mm2,综合性能达国际领先水平:频率捕获速度高达19.8 Gb/s/μs,是同类研究的两倍以上;能量效率低至0.41 pJ/bit,新增模块仅贡献0.02 pJ/bit能耗;PRBS31输入下误码率低于10-12,8GHz恢复时钟的RMS抖动仅445 fs。该成果为高性能计算、汽车以太网、闪存接口、PCIe Gen6等多场景高速串行链路提供了低功耗、高可靠的核心芯片解决方案,也为相关领域的技术升级提供了有力支撑。

论文第一作者为2022级硕士研究生冯丽妍,指导老师熊晓明教授、张钊研究员等人。广东工业大学集成电路学院是论文第一单位。

[1] Feng, Liyan; Li, Tuo; Zou, Xiaofeng; Xiong, Xiaoming; Zhang, Zhao. A 6-64-Gb/s 0. 41-pJ/Bit Reference-Less PAM4 CDR Using a Frequency-Detection-Gain-Enhanced PFD Achieving 19. 8-Gb/s/μs Acquisition Speed. IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II-EXPRESS BRIEFS, 2025, 72(1):68-72.