我院熊晓明教授团队在集成电路与系统设计领域的国际权威期刊《IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS》(TVLSI)发表研究论文,题为《Efficient Design Space Exploration for the BOOM Using SAC-Based Reinforcement Learning》。

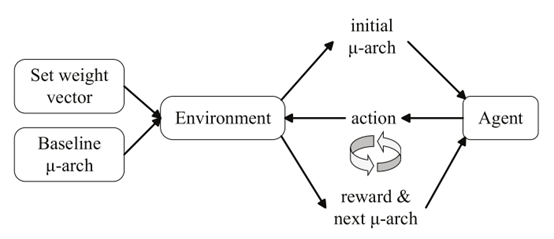

随着 RISC-V 指令集架构的迅速发展,设计空间探索(DSE)对于优化 CPU 微架构的性能、功耗和面积(PPA)十分重要。像传统的微架构 DSE 往往复杂且耗时。现有的机器学习方法虽能应对微架构DSE问题,但往往会依赖大量训练数据或受限于预定义的修改顺序,导致探索灵活性不足且面临高维动作空间和稀疏奖励的问题。针对这一挑战,团队提出了一种基于离散 Soft Actor-Critic(SAC)框架的强化学习方法,该方法能够动态选择和优化微架构参数,增强了设计空间探索的灵活性而无需依赖预定义的修改序列,同时通过引入了熵最大化策略进行高效探索,并集成了多步时序差分学习、经验回放缓冲区以及回报归一化技术,有效解决了高维动作空间下的样本效率低和学习不稳定的问题。研究结果表明,与现有最先进的方法相比 SAC-DSE 方法在样本效率上表现更佳,取得了优越的性能,展示了其在微架构 DSE 中的有效性和效率。此外,该方法通过对 PPA 指标的归一化技术,使所获得的设计点符合用户偏好的基础上,其 PPA 指标全面优于基准设计,为复杂的微架构DSE提供了高效方案。

在实际应用方面,团队成功验证了该方法能够更好地适应复杂的微架构 DSE ,能够对复杂的微架构参数组合进行优化。能依据用户设定的偏好,生成定制化的处理器设计方案。这项研究为解决复杂的微架构 DSE 中提供了创新解决方案,展现了其在集成电路 EDA 设计领城的广阔应用前景。

本论文的第一作者为广东工业大学集成电路学院2022级硕士研究生程名峻,广东工业大学集成电路学院郑欣副教授和蔡述庭教授为论文的通讯作者。广东工业大学集成电路学院为论文的第一完成单位。

[1] Cheng, Mingjun; Zhang, Shihan; Zheng, Xin; Lin, Xian; Gao, Huaien; Cai, Shuting; Xiong, Xiaoming; Yu, Bei. Efficient Design Space Exploration for the BOOM Using SAC-Based Reinforcement Learning. IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, 2025, 33(8):2252-2263.