近日,我院微纳电子器件与集成技术团队在薄膜晶体管研制、半导体器件表征等领域取得系列重要进展,在IEEE Transactions on Electron Devices、Applied Physics Letters等国际电子器件权威期刊上发表系列成果。

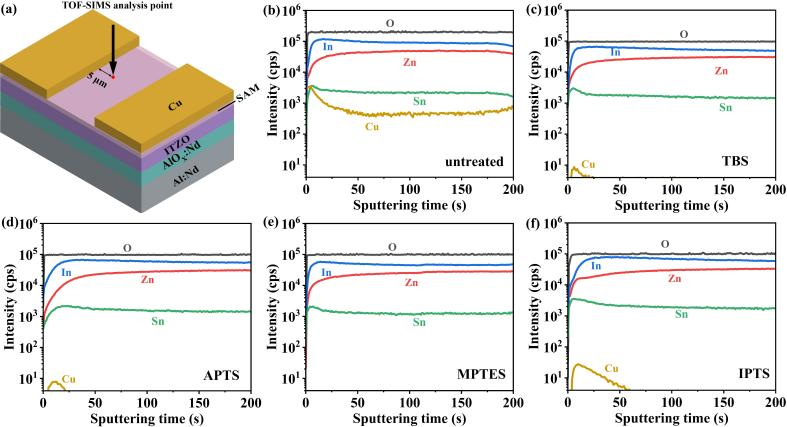

(1)基于非晶氧化物材料的DRAM是开启3D DRAM存储领域的重要技术,其商业化的核心在于如何降低金属-非晶氧化物界面接触电阻率。微纳电子器件团队通过构建多功能自组装单分子层SAMs作为Cu互连阻挡层(图1),有效降低金属-非晶氧化物界面接触电阻,为DRAM制造技术的发展提供了一种全新的可能,相关的论文发表在国际电子器件顶级期刊IEEE Transactions on Electron Devices(2024, 71(4): 2446-2451)上,硕士生陆浩冬为本文第一作者,钟伟副教授、刘远教授为本文的通讯作者。

图1 SAMS作为Cu电极扩散阻挡层研究

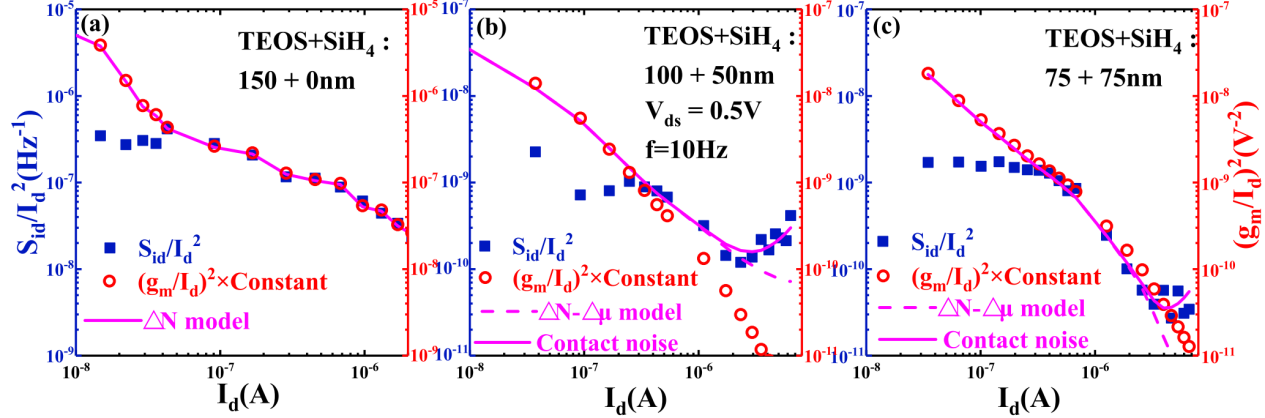

(2)通过低频噪声特性,微纳电子器件团队成功分离提取半导体器件内部微观电学缺陷信息,构建完整的半导体器件缺陷态表征技术,探讨引起器件电学参数退化的各项物理机制,并将该分析方法应用于半导体器件的工艺优化指导、可靠性评估等方面。相关的论文发表在微电子领域高水平期刊Applied Physics Letters (2024, 124(2): 023501, 图2)、IEEE Journal of the Electron Devices Society (2024,DOI:10.1109/JEDS.2024.3375867) 等上。青年教师陈雅怡为上述论文的第一作者,刘远教授、钟伟副教授为上述论文的通讯作者。

图2 栅氧化层对薄膜晶体管低频噪声的影响

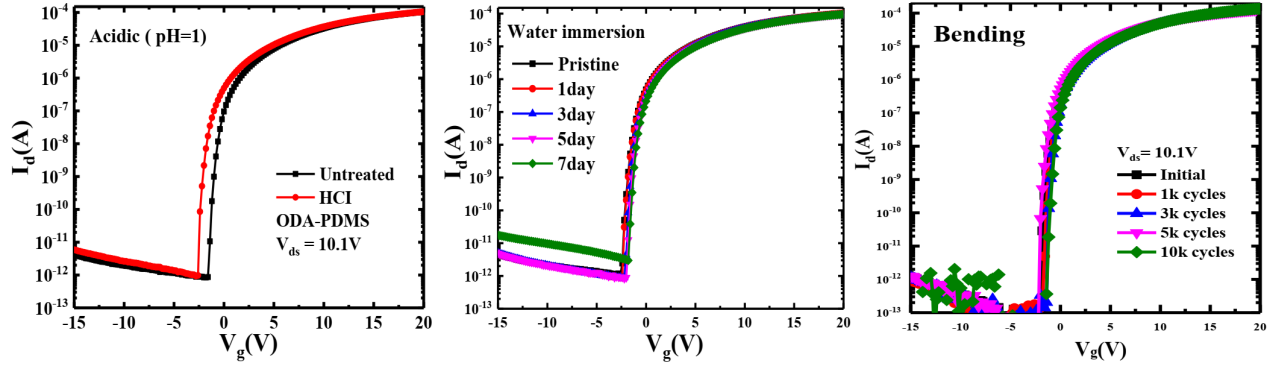

(3)微纳电子器件团队基于自组装技术构建具备超疏水功能的柔性钝化层。通过对钝化层内在结构、表面形貌与表面能的调控与优化,制备具有超疏水表面的自组装钝化层;这不仅显著改善半导体器件的本征电学可靠性,还能够提升半导体器件在高湿度、高酸碱度等极端运行环境中的可靠性。相关的论文发表在国际电子器件顶级期刊IEEE Transactions on Electron Devices (2023, 70(12): 6387-6392, 图3,图4)上。青年教师陈雅怡为上述论文的第一作者,刘远教授、钟伟副教授为上述论文的通讯作者。

图3 超疏水钝化层的构建过程

图4 超疏水钝化层改善器件在极端环境中的可靠性