近期,广东工业大学集成电路学院在微电子器件研究领域取得重要进展,研究成果“Gate Dielectric Treated by Self-Assembled Monolayers (SAMs) to Enhance the Performance of InSnZnO Thin-Film Transistors[1]”在微电子器件领域权威期刊IEEE Transactions on Electron Devices上发表。集成电路学院钟伟博士为该论文第一作者,刘远教授及华南理工大学陈荣盛教授为论文通讯作者。

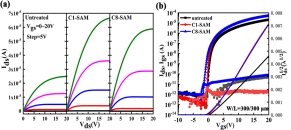

氧化物半导体具有迁移率高、大面积均匀性好和沉积温度低等优点,因此,基于氧化物半导体的薄膜晶体管 (TFT)为业界所广泛关注。然而,电介质/沟道界面的缺陷/陷阱可能会显著降低器件性能,包括电流开/关比、迁移率和稳定性。因此,系统开展器件界面工程研究对于提高TFT性能具有重要意义。

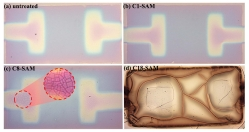

SAM处理是有机 TFT 中用于减少电介质/沟道界面陷阱和表面能的标准工艺。由于高温等工艺条件可能会对SAM产生潜在损害,因此SAM 处理在氧化物 TFT 中很少被报道。钟伟博士创造性提出了新型界面钝化方法:通过严格选择 SAM 并仔细控制沉积条件,以气相自组装工艺钝化介电/沟道界面陷阱,优化界面特性,进而提高器件性能。

[1] Zhong Wei, Zhang Jianfeng, Liu Yuan, Tan Lijun, Lan Linfeng, Deng Sunbin, et al. Gate Dielectric Treated by Self-Assembled Monolayers (SAMs) to Enhance the Performance of InSnZnO Thin-Film Transistors. IEEE Transactions on Electron Devices, 2022, 69(5): 2398-2403.