近期,我院在超大规模集成电路研究领域取得重要进展,研究成果“BSSE: Design Space Exploration on the BOOM With Semi-Supervised Learning[1]”在超大规模集成电路领域权威期刊IEEE Transactions on Very Large Scale Integration (VLSI) Systems上发表。我院郑欣副教授为该论文第一作者,熊晓明教授及蔡述庭教授为论文通讯作者。

处理器微架构的优化是当前应对摩尔定律放缓的途径之一。然而当前处理器微架构的设计与调优主要依赖设计者的经验,导致所设计的处理器微架构通常与最优解之间存在很大差距。另一方面,处理器的设计周期长,自动化程度低,不利于处理器的迭代优化。因此,优化处理器微架构设计空间探索的方法对于处理器的迭代升级具有重要意义。

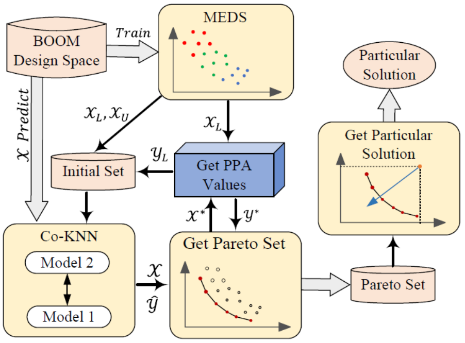

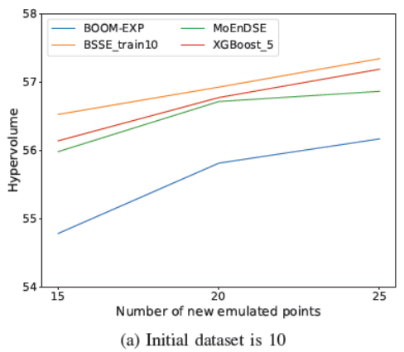

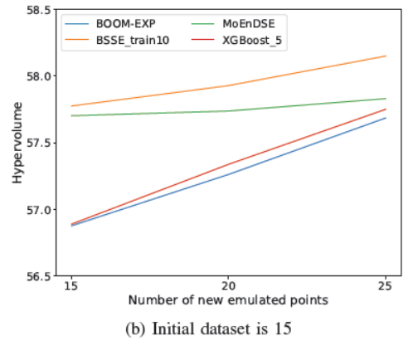

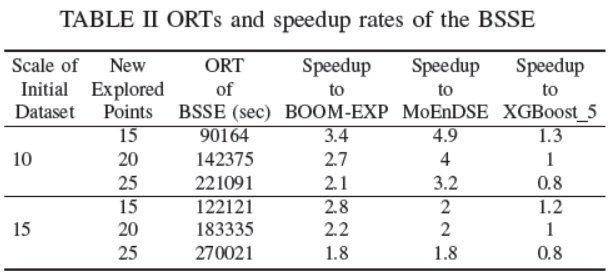

半监督学习是机器学习的其中一种方法,能结合有标签和无标签的数据来实现结果的预测,降低对有标签数据的依赖,同时有利于处理器设计的自动化。郑欣副教授创造性地将半监督学习应用于RISC-V处理器的多目标设计空间探索中,结合RISC-V处理器的设计经验和并行仿真方法,有效地优化了RISC-V处理器微架构的性能、功耗和面积,大幅度缩短了RISC-V处理器的设计周期。

[1]X. Zheng, M. Cheng, J. Chen, H. Gao, X. Xiong and S. Cai, "BSSE: Design Space Exploration on the BOOM With Semi-Supervised Learning," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, doi: 10.1109/TVLSI.2024.3368075.