近日,我院在大数模乘硬件加速领域取得重要进展,研究成果“FLALM: A Flexible Low Area-Latency Montgomery Modular Multiplication on FPGA”在《IEEE Transactions on Computers》上发表。这是我院首次以第一作者单位在TC上发表论文,充分展示了广工在数字集成电路设计领域的积累和科研实力。我院博士研究生谢宇俊为该论文第一作者,刘远教授及蔡述庭教授为论文通讯作者。

《IEEE Transactions on Computers》是IEEE在计算机领域最具影响力的期刊之一,也是中国计算机学会(CCF)的A类推荐期刊。该期刊创办于1952年,是计算机领域历史最悠久的期刊之一,每年发表论文仅200余篇,投稿录用率不足10%。

大数模乘是RSA、椭圆曲线密码、半同态和全同态等众多公钥密码学算法中最关键的运算之一,其对芯片性能与面积影响极大。蒙哥马利模乘算法是目前被应用最广泛的大数模乘算法。

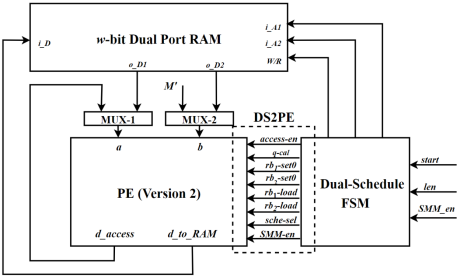

图1 FLALM硬件结构图

该论文提出了一种可扩展精度、低面积-延时的蒙哥马利模乘算法硬件加速器(FLALM),该加速器同时支持模平方运算,创新点包括:

1.一种新的基于FIPS(finely integrated product scanning)模乘的模平方调度算法,该算法仅需要新增少量控制便能使FIPS模乘支持模平方运算;

2.一种新的双调度方法,该方法解决了单运算引擎在高性能场景下算法数据竞争的问题;

3.低延时-面积硬件结构:该结构采用了电路复用和并行计算的硬件加速方法,平衡了各个关键路径的延时,关键算子Karatsuba Multiplication和Interative Compressor的利用率在连续运算过程中均接近100%。

通过在FPGA(Virtex-7平台)上的实现结果表明:在计算1024位和2048位GMM时,FLALM的面积*延迟(AL)值比目前最先进的可扩展参考方案提高了38.1%和44.7%;在计算SMM时,AL值的优势分别提升至73.7%和86.3%。

[1] Y. Xie, Y. Liu, X. Zheng, B. Lan, D. Lei, D. Xiang, S. Cai, and X. Xiong, “FLALM: A Flexible Low Area-Latency Montgomery Modular Multiplication on FPGA,” IEEE transactions on Computers, 2024. 10.1109/TC.2024.3457739.