2024年IEEE超大规模集成电路国际研讨会(IEEE Symposium on VLSI Technology and Circuit,VLSI Symposium)于6月16-20日在美国夏威夷开幕。VLSI Symposium 是与国际固态电路会议(ISSCC)、国际电子器件会议(IEDM)并称微电子技术领域的三大“奥林匹克盛会”,也是超大规模集成电路和半导体器件领域里最顶尖的国际会议之一。该会议在国际集成电路、半导体器件领域的学术界和工业界享有很高的学术地位和广泛影响,汇集了每年半导体业界和学术界最顶尖的研究成果。

我院郭春炳教授团队的论文“A 9-GHz Subsampling-Chopper PLL with Charge-Share Cancelling and Achieving 57.8fs-rms Jitter with 15dB In-band Noise Improvement”入选本届VLSI Symposium。论文的第一作者为博士生孔祥健,通讯作者为郭春炳教授。这是广东工业大学首次作为论文第一单位入选VLSI Symposium。据悉,本次VLSI Symposium中国内地共录用论文33篇,中国内地整体论文接收率为15.2%。

在物联网领域,高精度信息的采集和高速传送将成为制约电子系统性能的关键技术。在郭春炳教授带领下,我院面向新一代物联网的智能信号链科研团队针对这些关键技术展开科研攻关,包括信号采集过程中的高速高精度模数-数模转换器技术(ADC/DAC)、低功耗射频收发芯片(RFIC)以及高可靠性的射频-封装-天线一体化射频模组技术等。

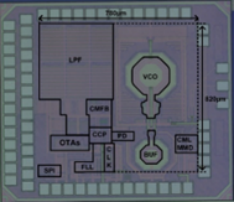

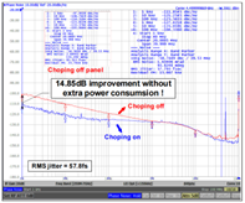

高性能时钟是射频及数模混合芯片中的关键模块。郭春炳教授团队一直致力于研发低抖动的高性能锁相环芯片(PLL)和倍频器芯片,为射频系统提供24 GHz到40 GHz的高性能时钟。团队研发的基于65 nm的欠采样锁相环芯片(SSPLL)性能达到了国际先进水平,此次入选VLSI Symposium 的论文展示了这一关键模块取得的成果。该成果在SSPLL的基础上在环路中引入了斩波技术将时钟抖动降低到极低水平(57.8 fs),这项技术将为射频芯片等系统提供优质的时钟信号源。

图1 SSPLL芯片和测试频谱