近日,集成电路学院熊晓明教授团队多项最新研究成果接连在国际顶级期刊IEEE Transactions on Computer-Aided Design of Integrated Circuits And System (TCAD)、Knowledge based Systems (KBS)和Design Automation for Embedded Systems (DAES)上发表。郑欣博士为论文第一作者,熊晓明教授为论文通讯作者。TCAD是集成电路领域公认的最具影响力的刊物之一,也是中国计算机学会推荐的A类期刊(CCF-A),主要发表集成电路和计算机辅助设计方向的最新研究成果,包括器件、电路及系统级的模型、算法、方法学和设计。KBS是计算机科学领域、特别是人工智能领域的国际一流期刊。DAES是涉及嵌入式系统系统设计的多学科期刊,在欧洲十分具影响力。该杂志主要关注嵌入式系统的工具、方法和体系结构,包括硬件/软件协同设计、仿真和建模方法、合成技术、体系结构和设计探索。

SoC软硬件协同设计相关研究正处在蓬勃发展的阶段。随着嵌入式系统的不断扩展,软硬件划分与机器学习,神经网络等新方法相结合已成为软硬件协同设计研究的热点之一,可以在保障划分质量的前提下,提高复杂系统软硬件划分速度。这些最新研究成果聚焦智能软硬件协同设计,不仅能加速芯片设计周期,而且还促进SoC设计方法学的发展。

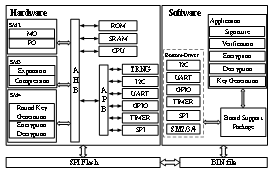

成果一:论文“The software/hardware co-design and implementation of SM2/3/4 encryption/decryption and digital signature system”发表在TCAD上。

智能设备的安全面临着巨大的挑战。作者提出了一种新的适用于此类设备的混合密码框架。采用软硬件协同设计的方法,实现了一种高效的基于SM2、SM3和SM4算法的加解密和数字签名方案。首先,根据纯软件解决方案的分析结果和设计约束条件下的硬件开销,将框架划分为软件部分和硬件部分。其次,通过软硬件协同设计实现了整个方案的流程和嵌入式算法。最后,提出了SM2/3/4算法的改进实现,以获得更高的效率。在该实现中,一些软硬件模块被并行化,从而减少了运行时间,提高了性能。所提出的设计是安全的,并且可以抵抗简单功率分析(SPA)攻击。特别是在数据传输和处理方面,采用了AHB接口IP和软件调度的方法。该设计采用中芯国际110 nm工艺流片。该芯片使用了大约199K个逻辑门和1mm2的面积。该芯片的工作频率为36 MHz,功耗为23 mW。与以往同类工作的比较表明,本文提出的设计具有更高的设计效率,执行速度提高了10%以上。

图1 软硬件协同设计数字签名系统SoC架构

图2 软硬件协同设计及优化性能结果图

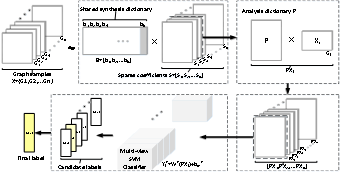

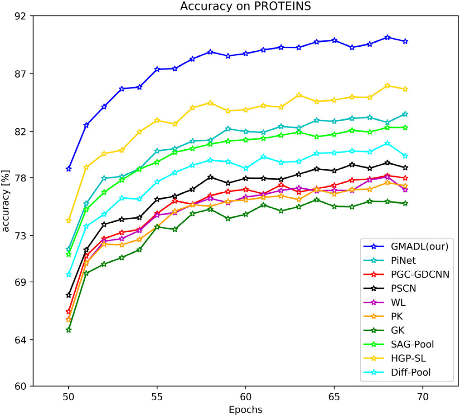

成果二:论文“Subgraph feature extraction based on multi-view dictionary learning for graph classification”发表在KBS上。

具有图结构数据的子图特征提取的效率问题日益突出。作者提出了一种新的子图特征提取体系结构——GMADL。作者搭建基于字典学习的多视角分类模型通过字典学习的方法来提取图数据的特征,以增强模型的识别性。为了提高特征提取的效率,分析词典被设计成直接生成稀疏代码的桥梁。每个稀疏码表示图的特征矩阵。通过构造多视点支持向量机分类器,将问题转化为多视点问题,利用整个视点的信息对分类模型进行预测。通过与现有方法的比较,证明了该方法的可行性和更好的分类性能,为后续将模型扩展到结点分类应用上提供了前期基础和十分有价值的参考。

图3 基于图结构的多视角分析字典学习模型

图4 分类精度结果图

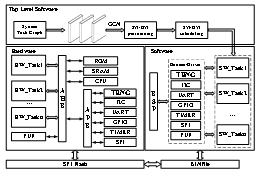

成果三:论文“A hardware/software partitioning method based on graph convolution network”发表在DAES上。

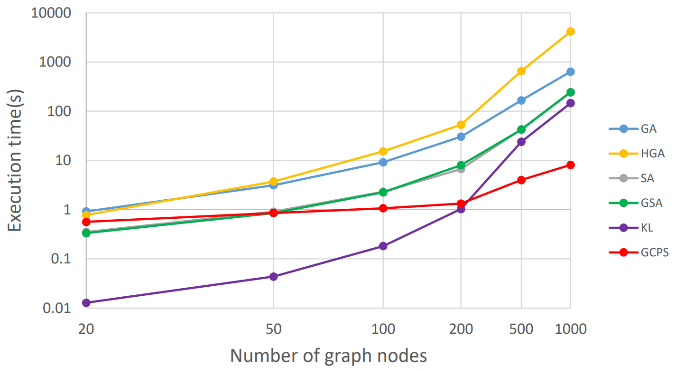

软硬件划分是软硬件协同设计中的关键步骤,它可以显著缩短嵌入式系统的上市时间,提高系统的性能。针对已有工作中探索时间长、生成的解质量不高的问题,提出了一种基于图卷积网络的软硬件快速划分方法——GCPS。它是一种新的基于GCN的划分方法,采用基于梯度的优化方法,可以极大地加快划分过程。为了量化解决方案的质量,调度被集成到划分过程中。实验结果表明,该方法不仅在效率上优于已有的元启发式算法(例如,对于1000个节点的任务图,比Kernighan-Lin算法快18倍),而且还提高了软硬件划分的质量(例如,对于1000个节点的图,加速比(AR)提高了10%以上)。

图5 嵌入式系统SoC架构

图6 软硬件划分时间结果图