Ø 团队简介

智能芯片及微体系结构设计科研团队依托广东工业大学集成电路学院成立。面向集成电路、人工智能等国家重大战略与行业市场需求,以新一代高密度智能芯片为研究核心,聚焦于高密度智能算法-硬件协同设计、FPGA与嵌入式系统、移动智能计算、基于后摩尔时代新器件的微体系结构设计与可靠性等领域的前沿基础理论和关键技术研究。团队主要开展“面向深度学习的智能硬件设计”、“热点智能应用软硬件协同”、“基于新器件的计算架构设计与可靠性”、“高性能微体系结构设计”等研究,承担国家自然科学基金、广东省自然科学基金等在内的多个国家级、省部级课题。团队研究成果相继在IEEE Transactions on Computers、IEEE Transactions on Very Large Scale Integration Systems、IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems、IEEE Transactions on Circuits and System I: Regular Papers、Design Automation Conference等国际权威期刊与会议上发表。

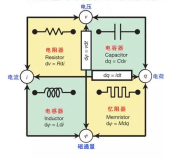

四种基本元件之间的关系 HP忆阻器的工作原理

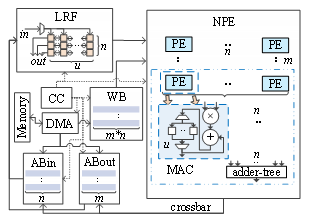

免搜索稀疏CNN后端综合版图 免搜索稀疏CNN加速计算架构

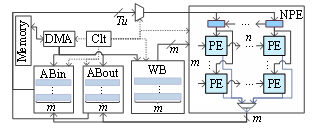

脉动阵列后端综合版图 面向深度学习的脉动阵列计算架构

Ø 团队核心成员

武继刚(教授、博士生导师)

研究领域:软硬件协同设计、VLSI容错及重构、移动智能计算

相继在国际著名学术期刊IEEE TC、TPDS、TVLSI等以及学术会议上发表学术论文300余篇;连续主持国家级、省部级等课题十余项。

郭龙坤(教授、博士生导师)

研究方向:电子设计自动化、算法设计与分析、组合优化

相继在国际著名学术期刊与会议IEEE TIT、TC、TCAD、TPDS、TMC、ICDCS与DAC等发表学术论文100余篇;主持多项国家级、省部级等课题。

吴亚兰(副教授、硕士生导师)

研究方向:微体系结构设计、移动智能计算

相继在国际著名学术期刊与会议IEEE TITS、Parallel Computing等发表学术论文30余篇;主持国家级、省部级课题。

刘鹏(副教授、硕士生导师)

研究方向:忆阻神经网络加速设计,忆阻逻辑设计与可靠性,基于忆阻器的微体系结构设计;

相继在国际著名学术期刊IEEE TETC、TCSI、TCSII等以及学术会议上发表学术论文10余篇。主持多项国家级、省部级课题。

刘博生(讲师)

研究方向:面向深度学习的智能硬件设计,智能算法-硬件协同设计,FPGA与嵌入式智能系统设计,计算机系统结构;

相继在国际著名学术期刊与会议IEEE TCAD、DAC、ASP-DAC等发表学术论文10余篇

Ø 主要研究方向

1.电子设计自动化

2.深度学习高密度硬件设计

3.高密度智能算法-硬件协同设计

4.忆阻神经网络加速设计、忆阻逻辑设计与可靠性

5.微体系结构设计、移动智能计算

Ø 代表性科研项目

1.郭龙坤. 云边协同环境中新型资源分配问题的组合优化算法与理论. 国家自然科学基金面上项目. 2023.1-2026.12.

2.刘鹏. 忆阻交叉阵列高质量低费用测试方法研究. 国家自然科学基金面上项目. 2022.1-2025.12.

3.武继刚. 片上网络高性能可重构设计与任务分配技术. 国家自然科学基金面上项目. 2017.1-2020.12.

4.武继刚. 可重构环境下软硬件协同设计算法研究. 国家自然科学基金面上项目. 2012.1-2015.12.

5.武继刚. 容错处理器网格的高效重构技术. 国家自然科学基金面上项目. 2010.1-2012.12.

6.武继刚. 面向3D视觉感知的人工智能芯片研发. 广东省科技计划重点领域研发项目. 2018.08-2021.08.